SD2068

- 产品特点

- 技术文档

| 总线 | 晶振 | VBAT脚 | 精度 | INT输出 | SRAM | 管脚可兼容 | 封装形式 | IIC | 外置 | √ | 外配 | √ | 12字节 | 1208/1307 | SOP8/TSSOP8 |

|---|

实时时钟IC SD2068

内置IIC总线接口、12字节SRAM、数字精度补偿寄存器

概述:

SD2068是一种具有标准IIC接口的实时时钟芯片,CPU可使用该接口通过5位地址寻址来读写片内32字节寄存器的数据(包括时间寄存器、报警寄存器、控制寄存器、通用SRAM寄存器)。SD2068内置单路定时/报警中断输出,报警中断时间最长可设至100年。 SD2068内置时钟精度数字调整功能,可以在很宽的范围内校正时钟的偏差(-189ppm~+189ppm,分辨力为3.05ppm),并通过外置的温度传感器可设定适应温度变化的调整值,实现在宽温范围内高精度的计时功能。该芯片可满足对实时时钟芯片的各种需要,为工业级产品,是在选用实时时钟IC时的理想选择。

主要性能特点:

>低功耗: 1.0μA 典型值(VBAT =3.0V,Ta=25℃)。

>工作电压:1.8~5.5V,工作温度:-40℃~+85℃。

>标准IIC总线接口方式,最高速度400KHZ(4.5V~5.5V)。

>年、月、日、星期、时、分、秒的BCD码输入/输出,并可通过独立的地址访问各时间寄存器。

>闰年自动调整功能(从2000年~2099年)。

>可选择12/24小时制式.

>内置年、月、日、星期、时、分、秒共7字节的报警数据寄存器及1字节的报警允许寄存器。

>内置12字节通用SRAM寄存器可用于存储用户的一般数据。

>三种中断均可选择从INT脚输出,并具有两个中断标志位.

>可设定并自动重置的单路报警中断功能(时间范围最长设至100年),年、月、日、星期、时、分、秒报警共有96种组合方式,并有单事件报警 和周期性报警两种中断输出模式.

>周期性频率中断输出:从32768Hz~1/16Hz……1秒共十五种方波脉冲.

>自动重置的8位倒计时定时器,可选的4种时钟源(4096HZ、64HZ、1HZ、1/60HZ)。

>内置时钟精度数字调整功能,可通过程序来调整走时的快慢。用户采用外置的温度传感器,设定适应温度变化的调整值,可实现在宽温范围内

高精度的计时功能。

>具有一个后备电池输入脚VBAT ,芯片依据不同的电压自动从VDD切换到VBAT或从VBAT切换到VDD。

>在VBAT模式下,芯片具有中断输出允许或禁止的功能,可满足在备用电池供电时输出中断的需要。

>内置IIC总线0.5秒自动复位功能(从Start命令开始计时),保证时钟数据的有效性及可靠性,避免IIC总线挂死问题。

>内置三个时钟数据写保护位, 避免对数据的误写操作,可更好地保护时钟数据。

>内置VBAT模式IIC总线通信禁止功能,从而避免在电池供电时CPU对时钟操作所消耗的电池电量,也可避免在主电源上、下电的过程中因CPU

的I/O端口所输出的不受控的杂波信号对时钟芯片的误写操作,进一步提高时钟芯片的可靠性。

>内置上电复位电路及指示位。

>内置电源稳压,内部计时电压可低至1.5V。

>芯片管脚抗静电(ESD)>4KV。

>芯片在兴威帆的评估板上可通过4KV的群脉冲(EFT)干扰。

>CMOS 工艺

>封装形式:SOP8/TSSOP8。

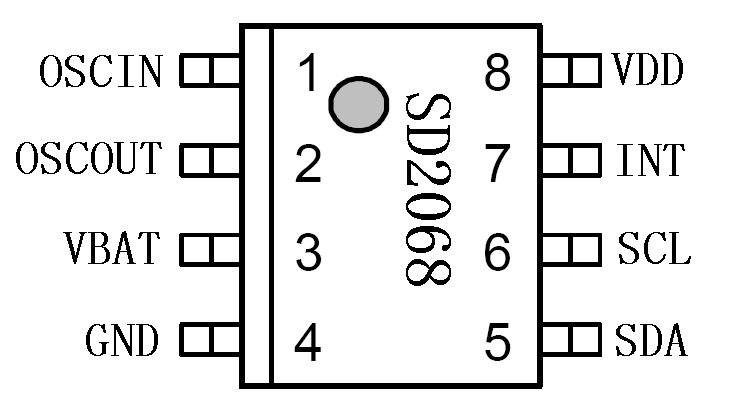

管脚设置:

管脚说明:

| 管脚 | 名称 | 功能 | 特征 |

| 1 | OSCIN | 晶振的输入 | 0~1.5V输入 |

| 2 | OSCOUT | 晶振的输出 | 0~1.5V输出 |

| 3 | VBAT | 备用电源(电池)输入脚.当VDD电源失效时VBAT为IC提供电源.(VBAT与电池之间的接法请参考芯片数据手册中的“应用参考电路”章节) | 1.5V~5.5V,不用时应将其接GND. |

| 4 | GND | 负电源(GND) | |

| 5 | SDA | 串行数据输入/输出脚,此管脚通常用一电阻上拉至VDD,并与其它漏极开路或集电器开路输出的器件通过线与方式连接. | N沟道开路输出, CMOS输入;当VBAT引脚的后备电源被激活时,该引脚被禁止. |

| 6 | SCL | 串行时钟输入脚,由于在SCL上升/下降沿处理信号,要特别注意SCL信号的上升/下降升降时间,应严格遵守说明书。 | CMOS输入. 当VBAT引脚的后备电源被激活时,该引脚被禁止. |

| 7 | INT | 报警中断输出脚,根据控制寄存器来设置其工作的模式,它可通过重写控制寄存器来禁止. | N-沟道开路输出 |

| 8 | VDD | 正电源 | 1.8V~5.5V |

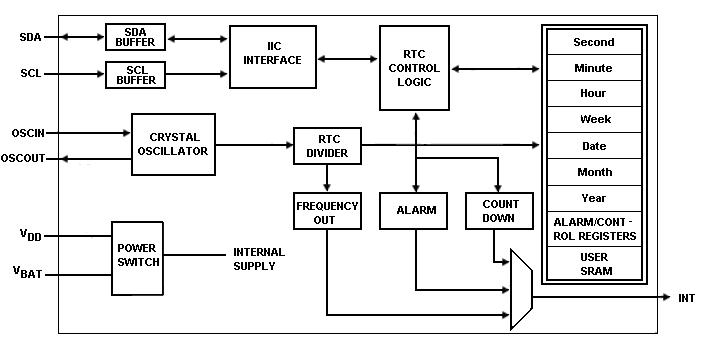

原理框图:

销售服务专线:0755-82127888

技术支持专线:0755-82127938

投诉专线:0755-82127989

0755-82127888

0755-82127888